嵌入式工程师

嵌入式工程师基础知识部分

一。进制转换

1)R进制转十进制

方法: 按权展开

- 二进制转十进制

$$

10100.01 = 1×2^4+1×2^2+1×2¯²

$$

- 八进制转十进制

$$

604 = 6×8^2+4×8^0

$$

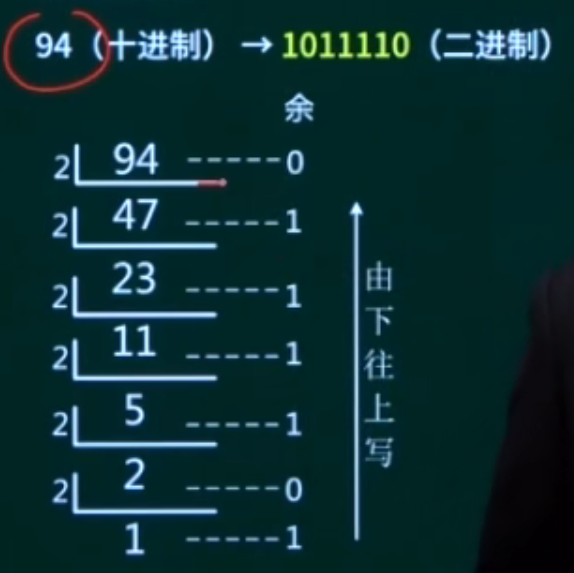

2)十进制转R进制

方法:短除法

二。数据的存储单位

- 位 b (bit比特)

- 字节 B (Byte)

1 | |

三。数的表示

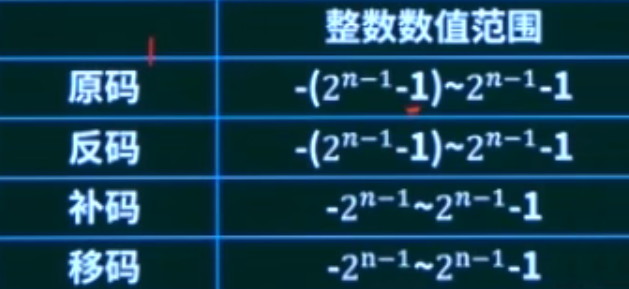

原码

反码:正数同原码,负数符号位不变,按位取反

补码:负数,符号位不变,原码从右往左第一个1后所有位取反

移码:补码符号位取反,其他不变

- 原码和反码表示范围比补码少一个

定点数和浮点数

1)定点数

小数点的位置固定不变

- 定点整数 : 用来表示整数(小数点位置在数字最低为后)

- 30 ——–> 0001110.

- 定点小数 : 用来表示纯小数(小数点在符号位和数值位之间)

- 0.875————> 0.1110000

.jpg)

- 浮点数运算

- 对阶

- 尾数计算

- 结果格式化

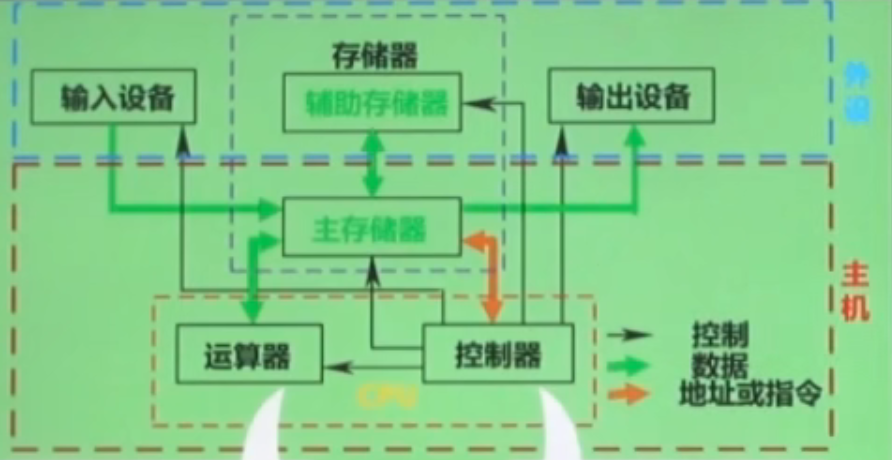

四。计算机的基本组成

1)输入设备(外设)

2)存储器

3)运算器(主机)

算数逻辑单位ALU:

- 数据的算术运算和逻辑运算

累加寄存器AC:

- 通用寄存器组成,为ALU提供一个工作区,用于暂存数据

数据缓冲寄存器DR

- 读写内存时,暂存指令或数据

状态条件寄存器PSW

- 存状态标志(如溢出标志)与控制标志

4)控制器(五大部件的控制协调,早期核心)(主机)

5)输出设备(外设)

- CPU: 运算器和控制器组成

CPU性能指标

- 主频

- 字长(32位,64位)

- CPU缓存

- 核心数量

总线的分类

一条总线同时只允许一个设备发送,但允许多个设备接受

数据总线(双向传输 CPU—>主存/主存—–>CPU)

- 在CPU与RAM之间来回传送需要处理或者需要存储的数据

地址总线(单向)

- 用来指定在RAM之中存储的数据的地址

控制总线(双向)

- 将微处理器控制单元的信号传送到周边设备

总线的性能指标

带宽 = 位宽 × 工作频率 (数据总量/总时间)

- 处理机由处理器、存储器和总线组成

BIOS/CMOS

- CMOS: 芯片(电池供电,保存计算机配置信息) RAM(可读写)

- BIOS: 程序(将配置信息进行修改写入CMOS) ROM

系统性能评测方法

- 时钟频率

- 指令执行

- 等效指令速度法

- 数据处理速度PDR

- 核心程序法

- 基准测试程序

指令系统

1)定义

指令: 一条指令就是机器语言的一个语句

是一组有意义的二进制代码

2)构成

操作码OP + 地址码字段A

- 操作码 : 指出计算机要执行什么性质的操作

- 地址码 : 包含各操作数的地址及操作结果的存放地址等

累加寄存器AC 程序计数器PC

4地址: A1 OP A2—>A3 A4—–>下一条指令地址

3地址: A1 OP A2—->A3 PC—–>下一条

2地址: A1 OP A2—–>AC PC—->下一条

1地址: AC OP A2 —-> AC

0地址: 出栈入栈 pop push

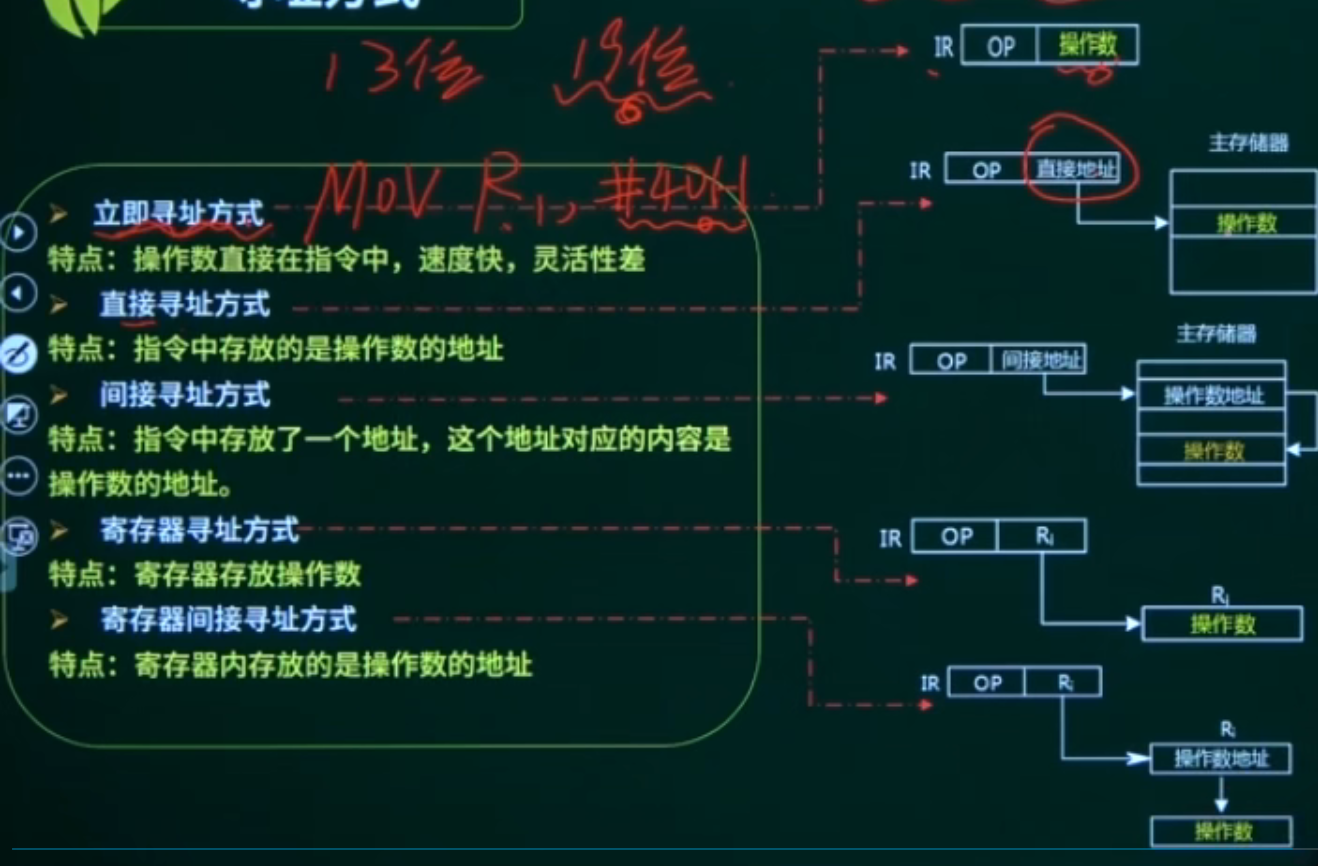

3)寻址方式

作用:

- 扩大寻址空间

- 提高编程灵活性

方式

- 立即寻址方式

- 操作数直接在指令中,速度快,灵活性差

- 直接寻址方式

- 指令中存放的是操作数的地址

- 间接寻址方式

- 指令中存放了一个地址,这个地址对应的内容是操作数的地址

- 寄存器寻址方式

- 寄存器存放操作数

- 寄存器间接寻址方式

- 寄存器内存放的操作数的地址

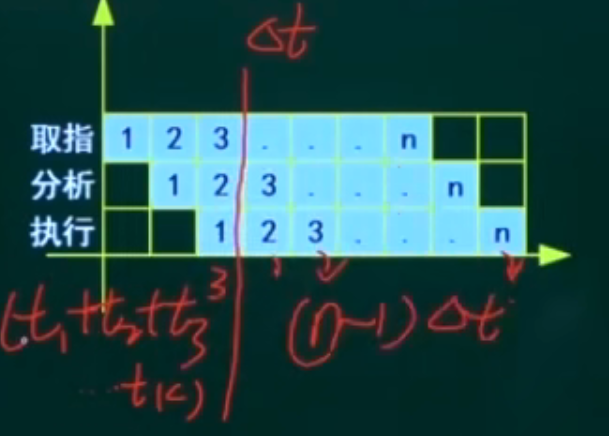

五。流水线

1)定义

多条指令重叠进行操作的一种准并行处理实现技术

2)指令执行的过程

取值 ———> 分析 ————-> 执行

3)流水线周期

定义:

执行时间最长的一段Δt

计算公式:

TK = 一条指令执行时间+ (指令条数-1)*流水线周期

流水线吞吐率

$$

TP = n/T_k

$$

- 单位时间内完成指令的条数

- 最大吞吐率,即为流水线周期的倒数 1/Δt

4)例题

流水线周期:执行时间最长的一段即为2ns

总时间:

$$

(2+2+1)+(100-1)*2=203ns

$$

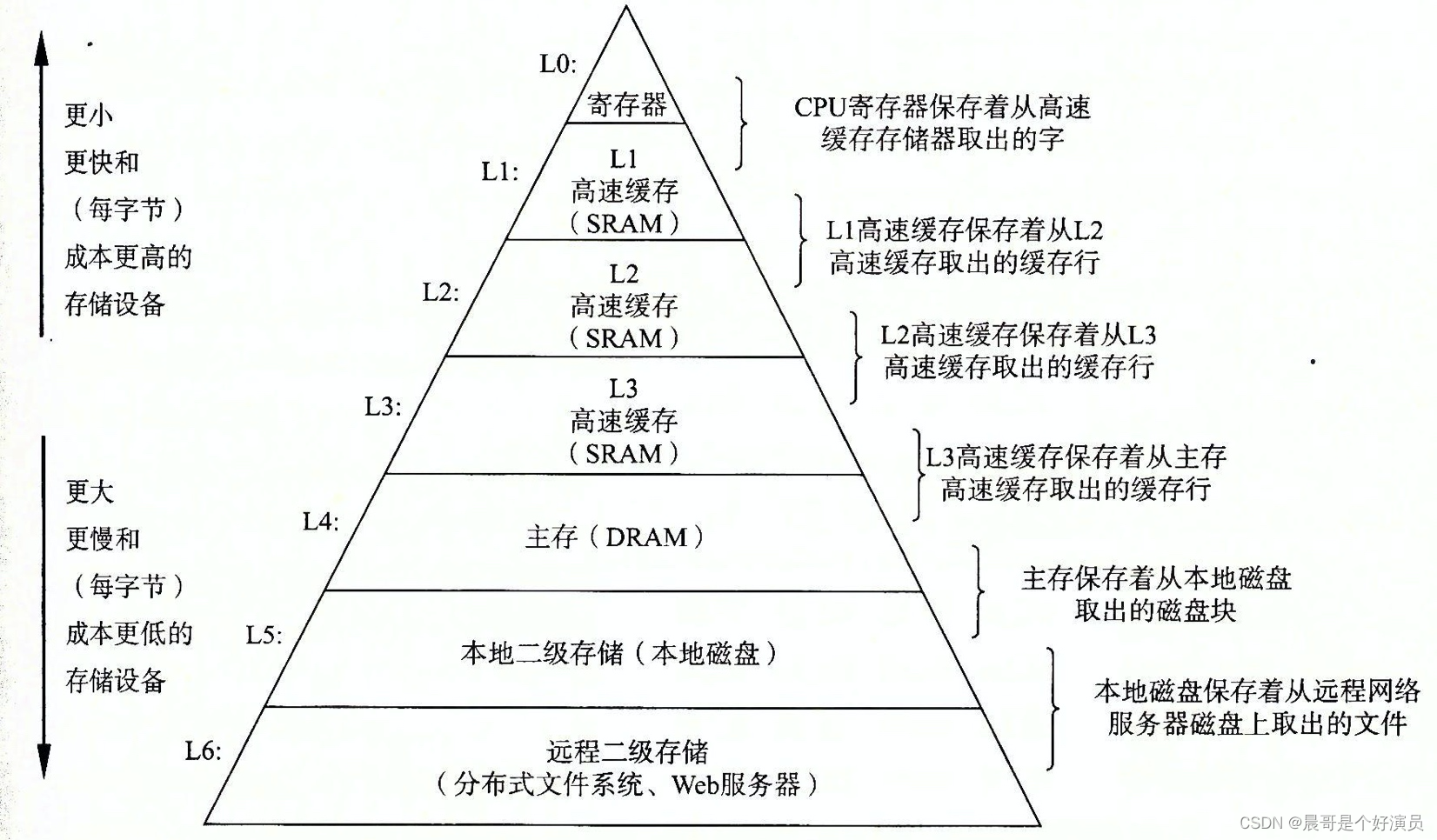

六。多级存储器结构

1)层级结构

自上而下,组成6个层次结构,依次变慢,访问效率更低,容量更大,价格更低

2)Cache

功能:提高CPU数据输入输出的速率

速度:计算机存储系统体系中,Cache是访问速度较快的层次

原理:局部性原理

- 空间局部性:一个内存位置被引用了一次,那么程序很可能在不远的将来引用其附近的一个内存位置。

- 时间局部性:被引用过一次的内存位置很可能在不远的将来再被多次引用。

组成:控制部分和Cache存储器部分

位置:介于CPU与内存之间

平均系统周期时间

$$

t_3=h*t_1+(1-h)*t_2

$$- h:Cache访问命中率

- t1: 访问Cache周期时间

- t2: 访问主存储器周期时间

- t3: 系统平均周期

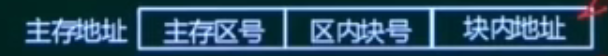

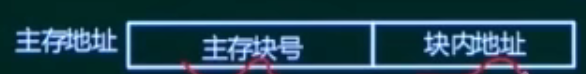

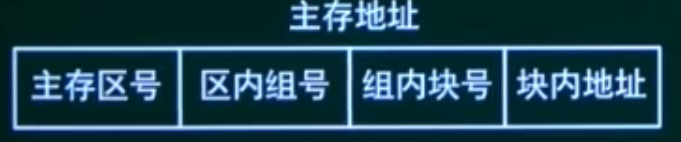

3)地址映像

1.直接映像

- 主存储器中一块只能映像到cache中一个特点的块中

- 主存与缓存分成相同大小的数据块

- 主存空间按缓存容量分成区,每一区的块数与缓存的总块数相等

- 主存中某区的一块存入缓存时只能存入缓存中块号相同的位置

特点

- 地址变换电路简单,访问速度快

- 空间利用率低,冲突概率高

- 对页面置换算法依赖度较高,且Cache空间利用率较低,命中率较低

2.全相联映像

- 主存中任意一块可以映像到cache中任意一块的位置上

- 主存和缓存分成相同大小的数据块

- 主存的某一数据块可以装入缓存的任意块空间中

特点

- 空间利用率高,命中率较高

- 冲突概率低

- 实现复杂,速度慢,适合小容量cache

3.组相联映像

- 主存和cache按相同大小分块

- cache分为若干组,如两块一组,主存按cache组数分区

- 每个组间采用直接映像方式

- 组内块采用全相联映像

特点

- 折中方法

- 实现难度和成本比直接映像高

七。 I/O控制

直接程序控制:

- 无条件传送方式

- 程序查询方式

中断方式

- 释放CPU,提高执行效率

直接存储器存取方式(DMA)

- 在传送数据块的过程中不需要CPU的干涉

- 是IO与主存之间传送数据的方式,数据不经过CPU

输入输出处理机(IOP)

- 有独立处理功能(用于大型处理机)

八。可靠性、检验码

可靠度计算

失效率 = 1- 可靠度

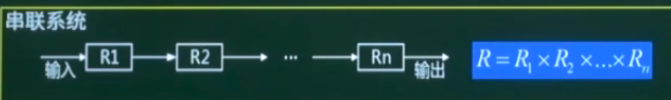

- 串联系统

- 并联系统

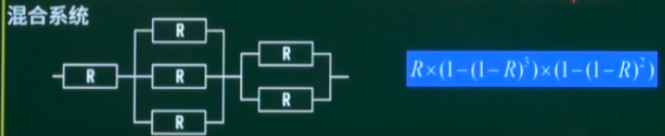

- 混合系统

校验码

码距

1

一个编码系统的码距就是整个编码系统中任意两个码字(合法编码)的最小距离奇偶校验码

- 可检测1位错

CRC(循环冗余码)

- 利用生成多项式为k个数据位产生r个校验位来进行编码(编码长度:k+r)

- 可检测多位错

- 模2运算

海明码

- 可纠正一位错

- 在数据位之间插入K个校验位,通过扩大码距来实现检查和纠错

- 数据位n位,校验位k位

$$

2^k -1 >= n+k

$$